2.4 原理图输入

在上一节我们练习了在Diamond里进行FPGA工程的整个流程,设计输入是通过编写硬件描述语言的形式。而Diamond也是支持原理图作为设计输入文件,对于数字电路的初学者来说更加直观,这里我们介绍一下Diamond中以原理图输入来建立工程。

2.4.1 新建一个工程

1,要实现原理图输入,我们要清楚项目的逻辑功能是如何实现。例如在这个例子里我们用原理图实现一个半加器,半加器是对两位二进制数做加法操作,他的真值表如下:

| 输入 加数A | 输入 加数B | 输出 和S | 输出 进位C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

根据真值表可以得到输入输出的逻辑关系:

S=!AB+A!B(!代表逻辑非)

C=AB

2,按照2.3.1节的步骤首先建立一个新的工程

2.4.2 输入原理图文件

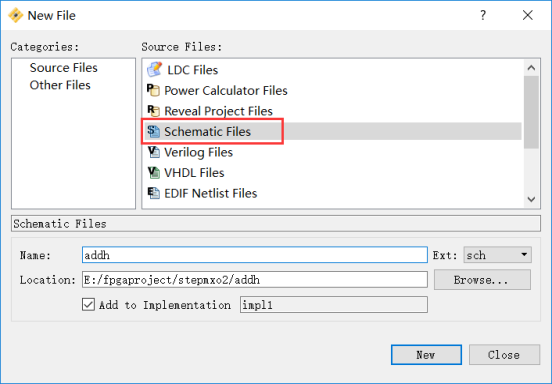

1,新建一个文件,选择Schematic Files

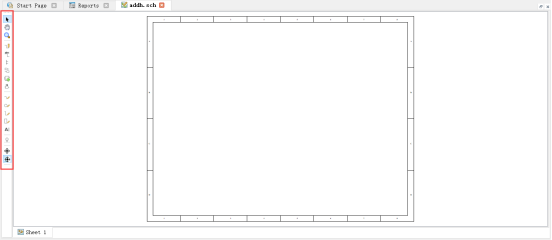

2,新建文件后会弹出原理图编辑窗口如下,左边是绘制原理图的快捷工具

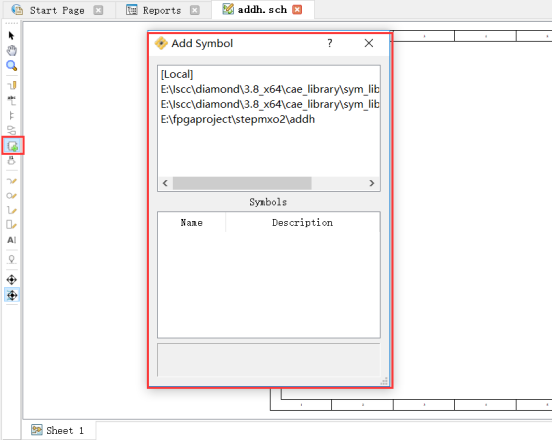

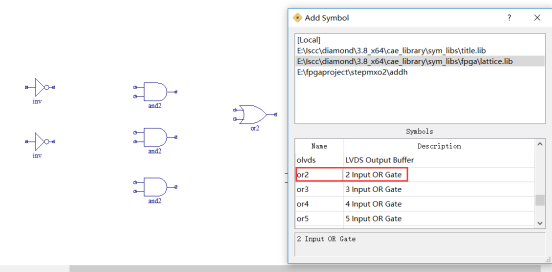

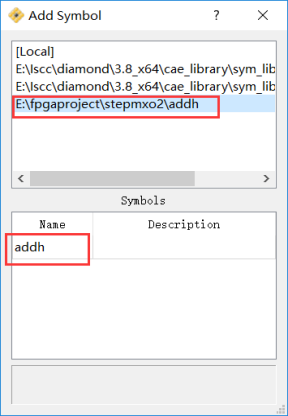

3,根据逻辑表达式开始绘制原理图,首先添加模块(Symbol),点击symbol 图标会弹出Add Symbol窗口。

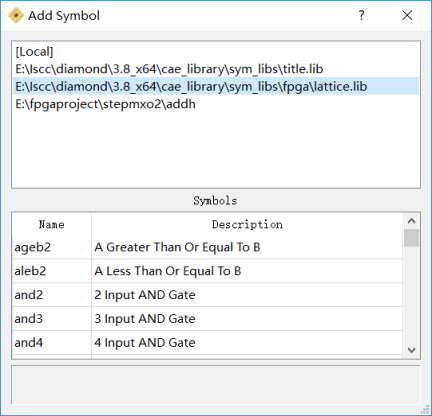

4,在Add Symbol窗口会看到有3个库文件,其中两个是软件默认库,一个是工程库,在lattice.lib库下面有很多常用的逻辑模块。

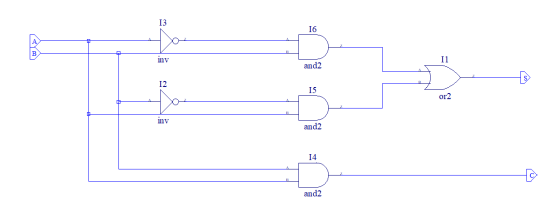

5,根据之前逻辑表达式我们先添加好逻辑门包括两个非门、3个与门以及一个或门。

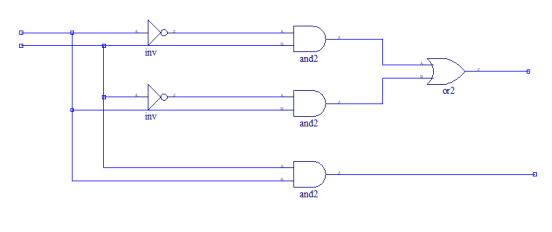

6,下面添加模块之间的连线,选择左边快捷工具栏上的wire,连接好个模块如下

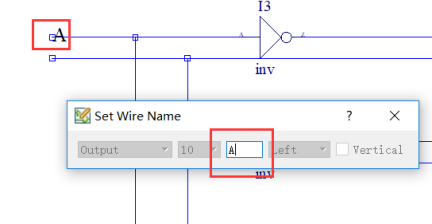

7,接下来定义信号的名称,点击左边快捷工具栏netname,如下图所示添加信号定义,鼠标点击信号端的小方块

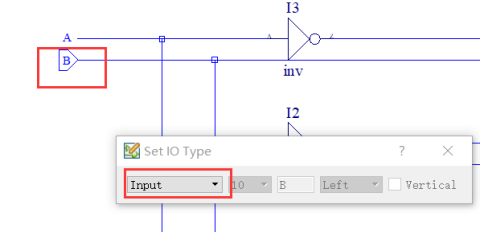

8,信号名称定义了以后设置输入输出状态,点击左边快捷工具栏IOport,如下图所示设置信号的输入输出状态

9,所有输入输出信号设置好了以后保存文件,到这里原理图输入完成。

10,按照2.3.3的步骤综合分配管脚,这里我们可以把输入设置成开关输入(M7,M8),输出信号到LED(N13,M12),这样一个半加器就完成。编译完成后可以下载到小脚丫板卡观察结果。

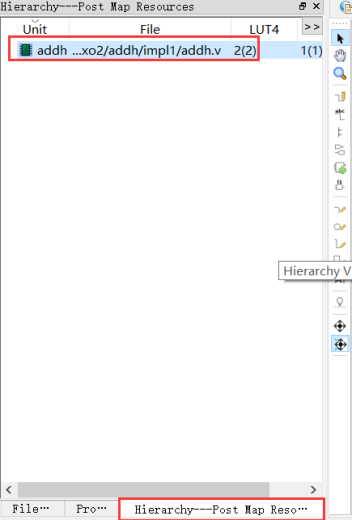

11,点击Hierarchy栏,会看到生成了一个Unit单元,这是软件根据原理图自动生成的verilog文件。

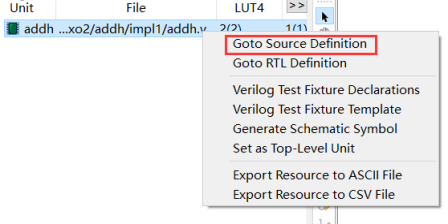

12,右键点击选择GoTo Source Definition可以查看源码内容。

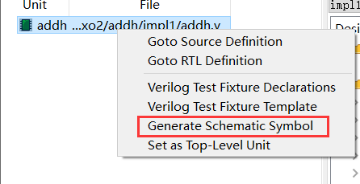

13,右键点击选择Generate Schematic Symbol可以生成一个新的模块Symbol

14,生成新的Symbol存入到了本地的器件库,以后可以在原理图编辑窗口添加重复利用。

2.4.3小结

在本节练习了如何进行原理图文件的输入、编辑。以及原理图和硬件描述语言之间互相引用编辑。